SRM University-AP preserves a research-empowered ecosystem stimulating its faculty and students to roll out original and discerning studies capable of making instrumental contributions aiming the scientific and societal progress. Making strides with impactful research publications and groundbreaking achievements, the institution has carved a niche for itself in the academic milieu. We are glad to present yet another success story of our research community that keeps bringing laurels to the institutions from far and wide.

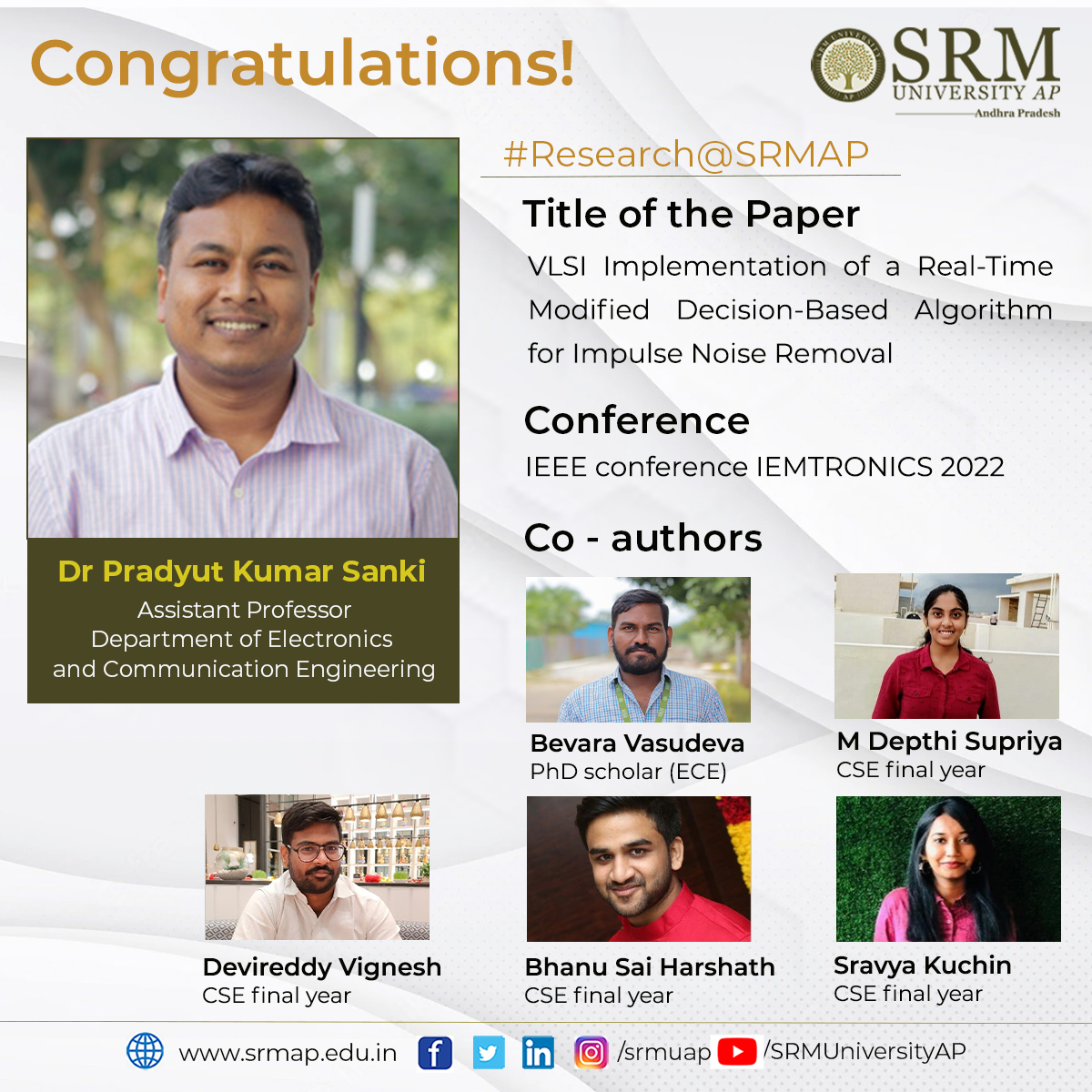

Dr Pradyut Kumar Sanki and his PhD scholar Bevara Vasudeva, from the Department of Electronics and Communications Engineering, along with a group of Computer Science and Engineering students: Medarametla Depthi Supriya, Devireddy Vignesh, Peram Bhanu Sai Harshath, and Sravya Kuchina have got their paper titled ‘’VLSI Implementation of a Real-Time Modified Decision-Based Algorithm for Impulse Noise Removal’’ accepted in the IEEE conference IEMTRONICS 2022. This publication is a part of the Capstone project contributed by the students.

IEMTRONICS 2022 (International IOT, Electronics and Mechatronics Conference) is an international conclave that aims to bring together scholars from different backgrounds to disseminate inventive ideas in the fields of IOT, Electronics and Mechatronics. The conference will also promote an intense dialogue between academia and industry to bridge the gap between academic research, industry initiatives, and governmental policies. This is fostered by panel discussions, invited talks, and industry exhibits where academia and industry will mutually benefit from each other.

Through the research paper, the team proposes a real-time impulse noise removal (RTINR) algorithm and its hardware architecture for denoising images corrupted with fixed valued impulse noise.

Abstract of the Research

A decision-based algorithm is modified in the proposed RTINR algorithm where the corrupted pixel is first detected and is restored with median or previous pixel value depending on the number of corrupted pixels in the image. The proposed RTINR architecture has been designed to reduce the hardware complexity as it requires 21 comparators, 4 adders, and 2 line buffers which in turn improve the execution time. The proposed architecture results better in qualitative and quantitative performance in comparison to different denoising schemes while evaluated based on the following parameters: PSNR, IEF, MSE, EKI, SSIM, FOM, and visual quality. The proposed architecture has been simulated using the XC7VX330T-FFG1761 VIRTEX7 FPGA device and the reported maximum post place and route frequency is 360.88 MHz. The proposed RTINR architecture is capable of denoising images of size 512 × 512 at 686 frames per second. The architecture has also been synthesized using UMC 90 nm technology where 103 mW power is consumed at a clock frequency of 100 MHz with a gate count of 2.3K (NAND2) including two memory buffers.