SRM University-AP publishes as the lead author among 21 co-authors from 13 countries

“Progress in Alternative Strategies to Combat Antimicrobial Resistance: Focus on Antibiotics” is a paper authored by Prof Jayaseelan Murugaiyan, Professor & Head, Department of Biological Sciences at SRM University-AP and his research scholar Ms Saranya Adukkadukkam, in Antibiotics Journal, having an impact factor of 4.639. It is a remarkable achievement that our university served as the first and the corresponding authors of this paper published in association with “Global AMR Insights Ambassadors Network”. A total of 21 co-authors from 13 countries (India, UK, France, The Netherlands, Switzerland, Italy, Spain, Ukraine, Lebanon, Egypt, Uganda, Bangladesh, and Nigeria) and six Indian universities (including SRM AP) participated in this work.

“Progress in Alternative Strategies to Combat Antimicrobial Resistance: Focus on Antibiotics” is a paper authored by Prof Jayaseelan Murugaiyan, Professor & Head, Department of Biological Sciences at SRM University-AP and his research scholar Ms Saranya Adukkadukkam, in Antibiotics Journal, having an impact factor of 4.639. It is a remarkable achievement that our university served as the first and the corresponding authors of this paper published in association with “Global AMR Insights Ambassadors Network”. A total of 21 co-authors from 13 countries (India, UK, France, The Netherlands, Switzerland, Italy, Spain, Ukraine, Lebanon, Egypt, Uganda, Bangladesh, and Nigeria) and six Indian universities (including SRM AP) participated in this work.

Antimicrobial resistance (AMR) – the ability of microorganisms to survive antimicrobials – is a global healthcare concern. AMR contributes to 1.27 million deaths among the 4.95 million deaths associated with bacterial AMR. If no control measures are taken, it is estimated that by 2050, it will claim the lives of 300 million people. The rise of these “superbug bacteria’s” – means that trivial medical interventions will soon become once again high-risk since no efficient antimicrobial chemotherapy is available. It is, therefore, crucial to understand the current situation and identify alternatives to combat the emergence and spread of antimicrobial resistance. This paper comprehensively discusses the alternative approaches that can be effectively utilised to combat AMR and, at the same time, without inducing further resistance among the pathogens. The paper has great social implications in making society aware of the scenario and encouraging the researchers to focus on alternative strategies to combat AMR.

Abstract of the paper: Antibiotic resistance, and, in a broader perspective, antimicrobial resistance (AMR), continues to evolve and spread beyond all boundaries. As a result, infectious diseases have become more challenging or even impossible to treat, leading to an increase in morbidity and mortality. Despite the failure of conventional, traditional antimicrobial therapy, in the past two decades, no novel class of antibiotics has been introduced. Consequently, several novel alternative strategies to combat these (multi-) drug-resistant infectious microorganisms have been identified. The purpose of this review is to gather and consider the strategies that are being applied or proposed as potential alternatives to traditional antibiotics. These strategies include combination therapy, techniques that target the enzymes or proteins responsible for antimicrobial resistance, resistant bacteria, drug delivery systems, physicochemical methods, and unconventional techniques, including the CRISPR-Cas system. These alternative strategies may have the potential to change the treatment of multi-drug-resistant pathogens in human clinical settings.

Global AMR Insight Ambassador Network: AMR Insights, an international network-based organisation interacting with professionals around the globe: in Human and Veterinary Health, Agri-food and Environment, was set up in 2017 following an in-depth feasibility study towards a new information platform on AMR. It mainly focuses on informing, educating and connecting people with the aim to curb antimicrobial resistance. Prof Jayaseelan Murugaiyan and Ms Saranya Adukkadukkam are members of the Global AMR Insights Ambassador Network.

Ms Saranya Adukkadukkam, the co-author from SRM AP says:

The guidance of Prof Jayaseelan Murugaiyan is the pillar of my research. His support and passion for research always encourage me. He gives importance to translational research and motivates me to stand unique in the field. He shows me a path where I can serve the people through research. Foreseeing my future as a scientist, he guides me to more opportunities to collaborate with international scientists. I feel proud of my mentor Prof Jayaseelan Murugaiyan for letting me fly. Also, I thank SRM University-AP for providing generous fellowship, excellent research facilities and ambience to carry out the research.

- Published in Biology News, Departmental News, News, Research News

Vision-based fall detection AI

Human-like care is difficult to replicate. Due to the lack of a reliable vision-based fall detection AI, it is often more effective to assign a lot of manpower towards vision-based detections that have not been efficiently implemented.

Ms Inturi Anita Rani, Research Scholar in the Department of Computer Science Engineering, working with her supervisor, Dr V. M. Manikandan, has worked on a paper titled, “A Novel Vision-Based Fall Detection Scheme using Keypoints of Human-Skeleton with Long Short-term Memory Network” in the Arabian Journal for Science and Engineering published by Springer with an Impact Factor of 2.33.

Abstract of the research:

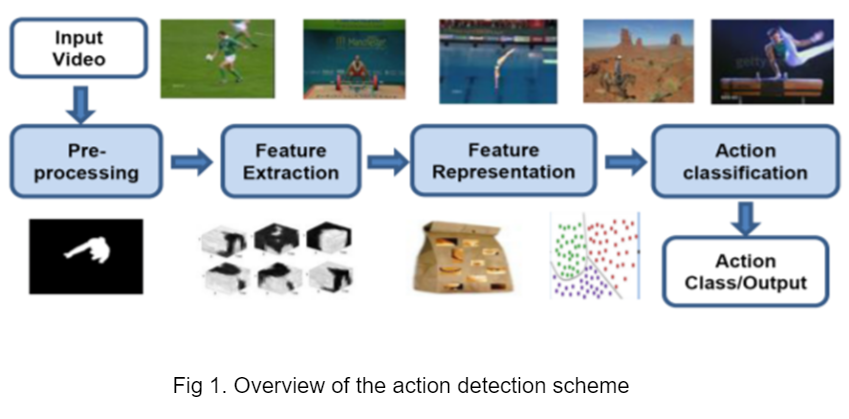

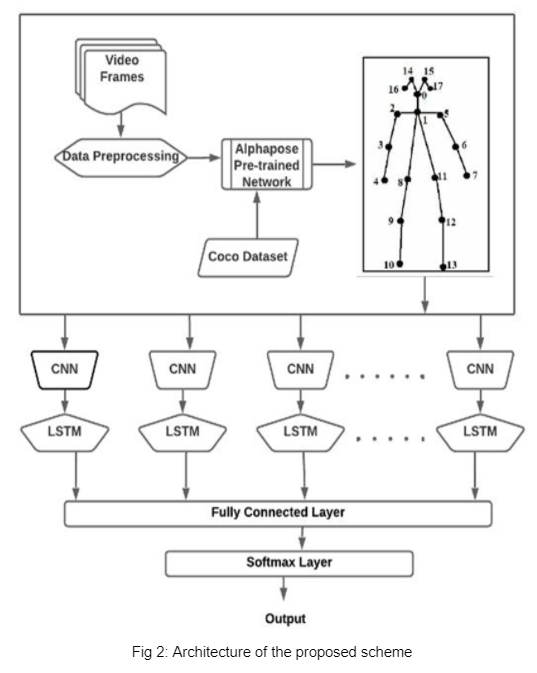

Humans are skilled at visually recognizing and classifying actions in videos, but it’s tough to automate this process. Human action detection in videos is useful in applications like automated surveillance, assisted living, human-computer interaction, content-based video retrieval, and video summarization. The ability to recognize atomic actions like “walking,” “bending,” and “falling” is critical for activity analysis when monitoring elderly people’s daily activities. Our paper presents a new promising solution for fall detection using vision-based approaches. In this approach, we analyse the human joint points which are the prime motion indicators. A set of keypoints of the subject are acquired by applying the AlphaPose pre-trained network. These keypoints are inferred to be the joint points of the subject. The acquired keypoints are processed through a framework of convolutional neural network (CNN) layers. Here, the spatial correlation of the keypoints is analysed. The long-term dependencies are then preserved with the help of long short-term memory (LSTM) architecture. Our system detects five types of falls and six types of daily living activities. We used the UP-FALL detection dataset for validating our fall detection system and achieved commendable results when compared to the state-of-the-art approaches. For comparison, we employed the OpenPose network for keypoint detection. It is inferred from the results that the AlphaPose network is more precise in keypoint detection.

About the research paper:

In this paper, the author proposes a vision-based system that is capable of detecting various types of falls accurately through video processing with the help of a machine learning approach.

Implementation of the research:

The proposed scheme can be used to monitor the activity of elderly people and if any unusual falls happen, the information can be shared with caretakers to ensure emergency services.

- Published in CSE NEWS, Departmental News, News, Research News

‘Super Randonneur’ title for SRM AP student, Saiprasad Koneru for remarkable talent in cycling

Amravati, February 16, 2022

Amravati, February 16, 2022

SRM University-AP’s Computer Science Engineering student Koneru Saiprasad won the ‘Super Randonneur’ title for his outstanding talent in cycling. Saiprasad recently set a new record for the longest distance cycling organized by Audax Club India with its headquarters in Guntur, shortly after reaching the target.

Saiprasad elaborated his quest with a beaming note, “On November 6, we cycled from Vijayawada to Nallajerla for 13 hours and then back to Vijayawada (200 km). Similarly, on November 27, he cycled from Vijayawada to Suryapeta on the Hyderabad route for 20 hours and then back to Vijayawada (300 km). He cycled from Vijayawada to Nakrekal for 27 hours on December 18 and back to Vijayawada (400 km). A week ago, he cycled from Guntur to Ramoji Film City and back to Guntur (600 km) in 40 hours, setting a record.”

Saiprasad won the ‘Super Randonneur’ title reserved for those who complete these four events. Saiprasad informed that he has loved cycling since he was a child and focused on long-distance cycling during lockdowns. He dedicated his achievement to his parents and university professors for their support and encouragement in all possible ways.

- Published in News, Students Achievements

Tenancy and Credit: Exploring Facts below the Crust in AP

SRM University-AP is proud to announce that Dr Ghanshyam Kumar Pandey, Department of Economics, has received the prestigious NABARD (National Bank for Agriculture and Rural Development) grant of Rs 14.85 lacs for a duration of 10 months of active research on “Tenancy and Credit: Exploring Facts below the Crust in AP”.

SRM University-AP is proud to announce that Dr Ghanshyam Kumar Pandey, Department of Economics, has received the prestigious NABARD (National Bank for Agriculture and Rural Development) grant of Rs 14.85 lacs for a duration of 10 months of active research on “Tenancy and Credit: Exploring Facts below the Crust in AP”.

About the Research

The study will attempt to identify different possible sources of credit of agriculture households in the Guntur district of AP and then an analysis of the impact at the macro level will be carried out. The role of self-help groups and microfinance on agriculture and livelihood will be one important component of this analysis. Transaction cost, cascading effect, and loan waiver impact will be estimated across tenant and owner cultivators, and social groups.

The study will help to understand the improvement in the life of tenants due to the adoption of the ‘Model Tenancy Act’ and provide feedback on the Tenancy Certificate introduced in AP for enabling farmers to access bank/formal credit and whether the formation of JLGs has led to increase in the credit availability to tenants or not.

The project will help understand the sociological impact of economic decisions by the governance and help direct policies to more beneficial outcomes especially in terms of Tenancy and Credit.

- Published in Departmental News, Economics Current Happenings, Economics News, News