Dr M Durga Prakash, Assistant Professor in the Department of Electronics and Communication Engineering, and his PhD scholar, Ms U Gowthami, have published a research paper titled “Performance Improvement of Spacer-engineered N-type Tree Shaped NSFET towards Advanced Technology nodes” in the Q1 journal, IEEE Access. The paper has an impact factor of 3.9 and will pave the way for significant advancements in the field.

Here’s an abstract of their research paper

Abstract:

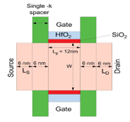

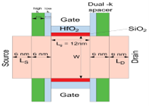

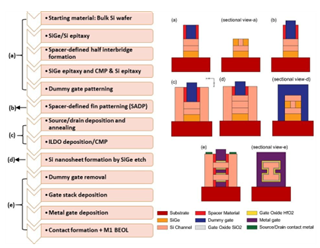

Scaling gate lengths deep is most reliable with tree-shaped Nanosheet FETS (NSFET). This paper uses TCAD simulations to study the 12nm gate length (LG) n-type Tree-shaped NSFET with a stack of high-k dielectric (HfO2) and (SiO2) spacers. The Tree-shaped NFET device features high on-current (ION) and low off-current (IOFF) with T(NS) = 5 nm, W(NS) = 25 nm, WIB=5nm, and HIB = 25 nm. Comparison of single- and dual-k spacer 3D devices and DC properties are shown. Because fringing fields with spacer dielectric prolong the effective gate length, the dual-k device has the highest ION / IOFF ratio, 109, compared to 107. This research also examines where work function, inter bridge height, breadth, gate lengths, temperature, and analog/RF and DC metrics affect the device. The suggested device has good electrical properties at 12 nm LG, with DIBL = 23 mV/V, SS = 62 mV/dec, and switching ratio (ION / IOFF) = 109. The device’s performance proves Moore’s law applies to lower technological nodes, enabling scalability.

The link to the article- https://ieeexplore.ieee.org/document/10499264 DOI: 10.1109/ACCESS.2024.3388504