Prof. Siva Sankar Yelampalli and Dr Ramesh Vaddi, Associate Professor, from the Department of Electronics and Communication Engineering, along with research scholars Mr Birudu Venu, Mr Tirumala Rao Kadiyam, and Mr Koteswara Rao Penumalli, have jointly published a paper titled “Computing in-memory reconfigurable (accurate/approximate) adder design with negative capacitance FET 6T-SRAM for energy efficient AI edge devices” The paper introduces Computing in-memory (CiM) as a promising alternative to traditional von-Neumann architectures, focusing on its potential for energy-efficient AI edge computing with CMOS scaling. Additionally, they have explored the advancements in approximate computing in-memory (ACiM) techniques, aiming to further enhance the energy efficiency of these innovative architectures.

Abstract:

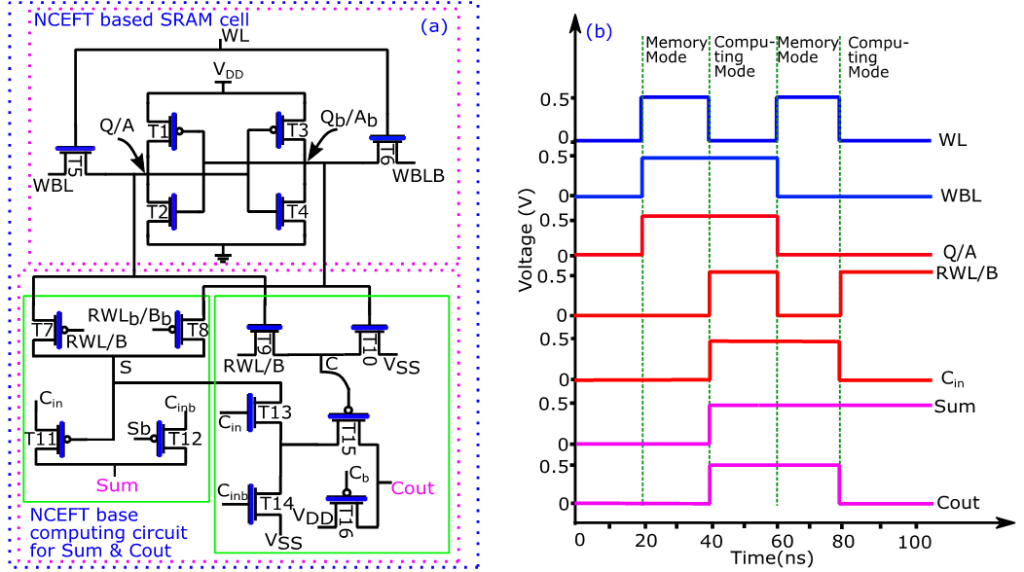

Computing in-memory (CiM) is an alternative to von Neumann architectures for energy-efficient AI edge computing architectures with CMOS scaling. Approximate computing in-memory (ACiM) techniques have also been recently proposed to further increase the energy efficiency of such architectures. In the first part of the work, a negative capacitance FET (NCFET) based 6T-SRAM CiM accurate full adder has been proposed, designed and performance benchmarked with equivalent baseline 40 nm CMOS design. Due to the steep slope characteristics of NCFET, at an increased ferroelectric layer thickness, Tfe of 3 nm, the energy consumption of the proposed accurate NCFET-based CiM design is ∼82.48% lower in comparison to the conventional/Non CiM full adder design and ∼85.27% lower energy consumption in comparison to the equivalent baseline CMOS CiM accurate full adder design at VDD = 0.5 V. This work further proposes a reconfigurable computing in-memory NCFET 6T-SRAM full adder design (the design which can operate both in accurate and approximate modes of operation). NCFET 6T-SRAM reconfigurable full adder design in accurate mode has ∼4.19x lower energy consumption and ∼4.47x lower energy consumption in approximation mode when compared to the baseline 40 nm CMOS design at VDD = 0.5 V, making NCFET-based approximate CiM adder designs preferable for energy efficient AI edge CiM based computing architectures for DNN processing.

Future research plans: Implementing reconfigurable computing in-memory (CiM) MAC for energy-efficient AI edge devices.