Recent News

- Paper accepted in the prestigious conference to be held in Caneda June 27, 2022

The research paper, An under complete autoencoder for denoising computational 3D sectional images from the Department of Electronics and Communication Engineering has been accepted in a prestigious conference called Imaging and Applied Optics Congress to be held in Vancouver, Canada 2022. Assistant Professors; Dr Sunil Chinnadurai, Dr Karthikeyan Elumalai, Dr Inbarasan Muiraj, and the PhD students; Ms Vineela Chandra Dodda and Ms Lakshmi Kuruguntla are the authors who contributed to composing the paper.

Abstract

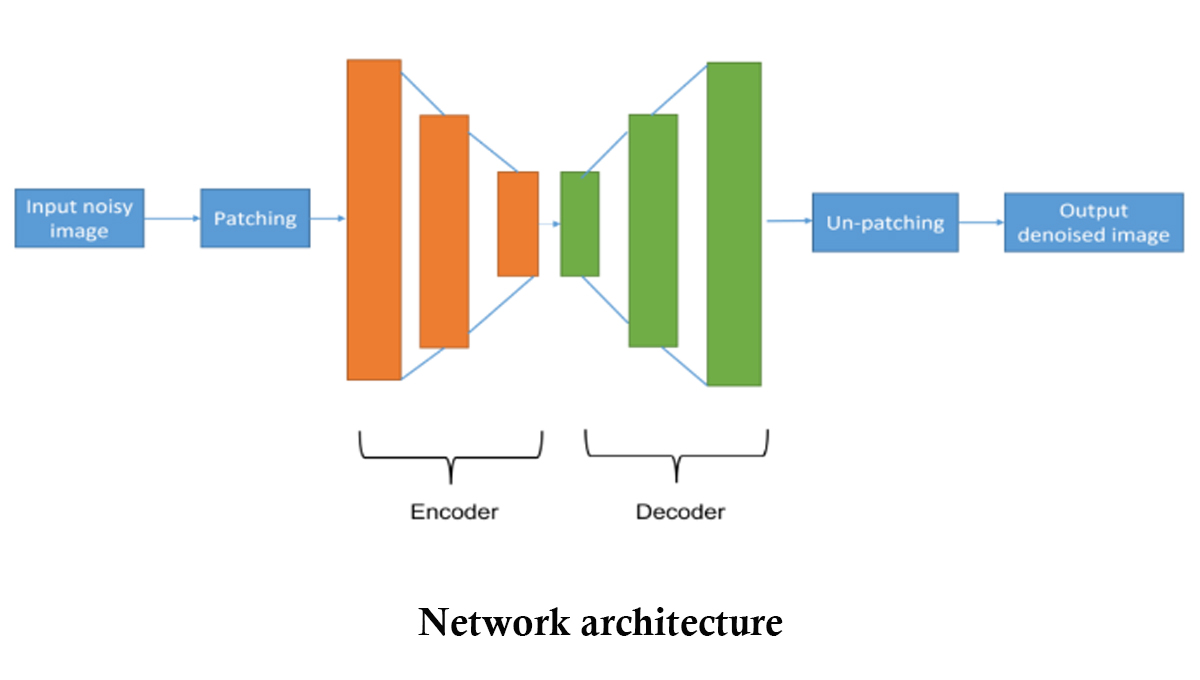

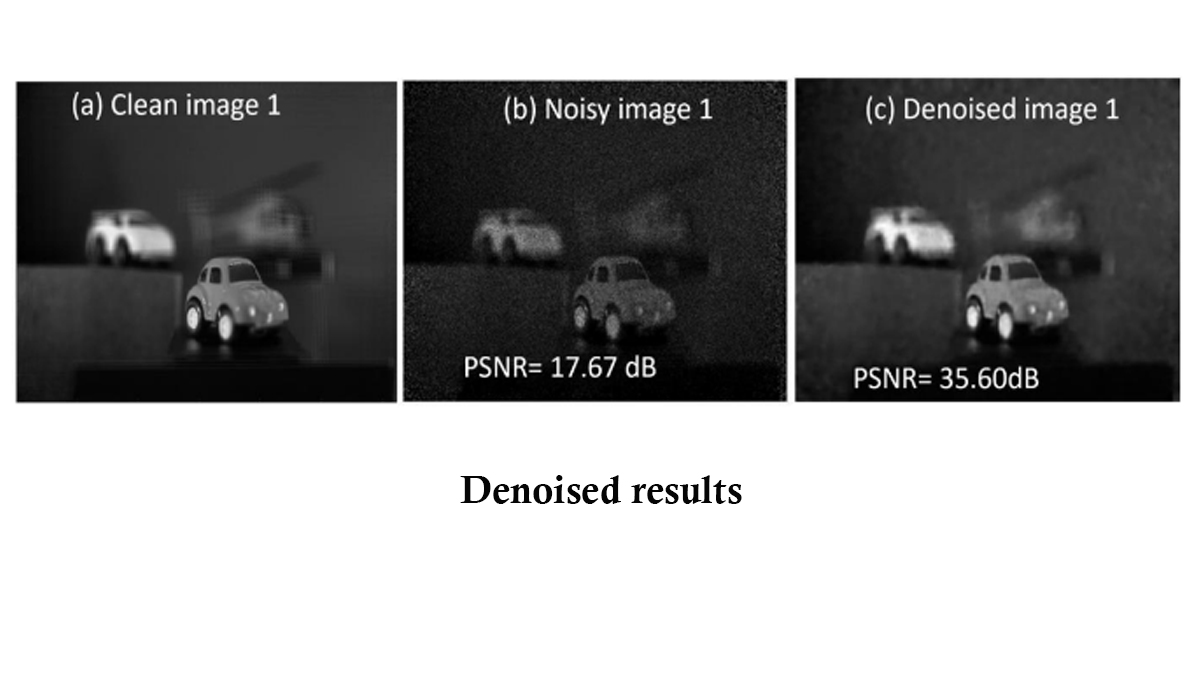

This paper proposes to use a deep-stacked under complete autoencoder to denoise the noisy 3D integral (sectional) images with a patch-based approach. In this process, the noisy input 3D sectional image is divided into multiple patches, which are then used to train the neural network. By using the patch-based approach, the time required to prepare the labeled training data is greatly reduced. Results demonstrate the feasibility of our proposed model in terms of the peak-signal-to-noise ratio.

This paper proposes to use a deep-stacked under complete autoencoder to denoise the noisy 3D integral (sectional) images with a patch-based approach. In this process, the noisy input 3D sectional image is divided into multiple patches, which are then used to train the neural network. By using the patch-based approach, the time required to prepare the labeled training data is greatly reduced. Results demonstrate the feasibility of our proposed model in terms of the peak-signal-to-noise ratio. Explanation of the research

Explanation of the researchDenoising is one of the preliminary processes in image processing that removes noise from an image of interest and restores a clean image. The noise which was generated during the image acquisition process is attenuated using deep learning techniques. The denoised image is further used in various tasks of image processing.

In any image acquisition system, noise is inevitable and needs to be attenuated before further processing for qualitative results. The medical field is an example of this (images acquired through CT, MRI, PET, etc.). The researchers further investigate various techniques in deep learning to improve the denoising performance along with the applicability of deep learning in various tasks such as object recognition etc.

Continue reading → - Deep learning enabled IRS for 6G intelligent transportation systems June 24, 2022

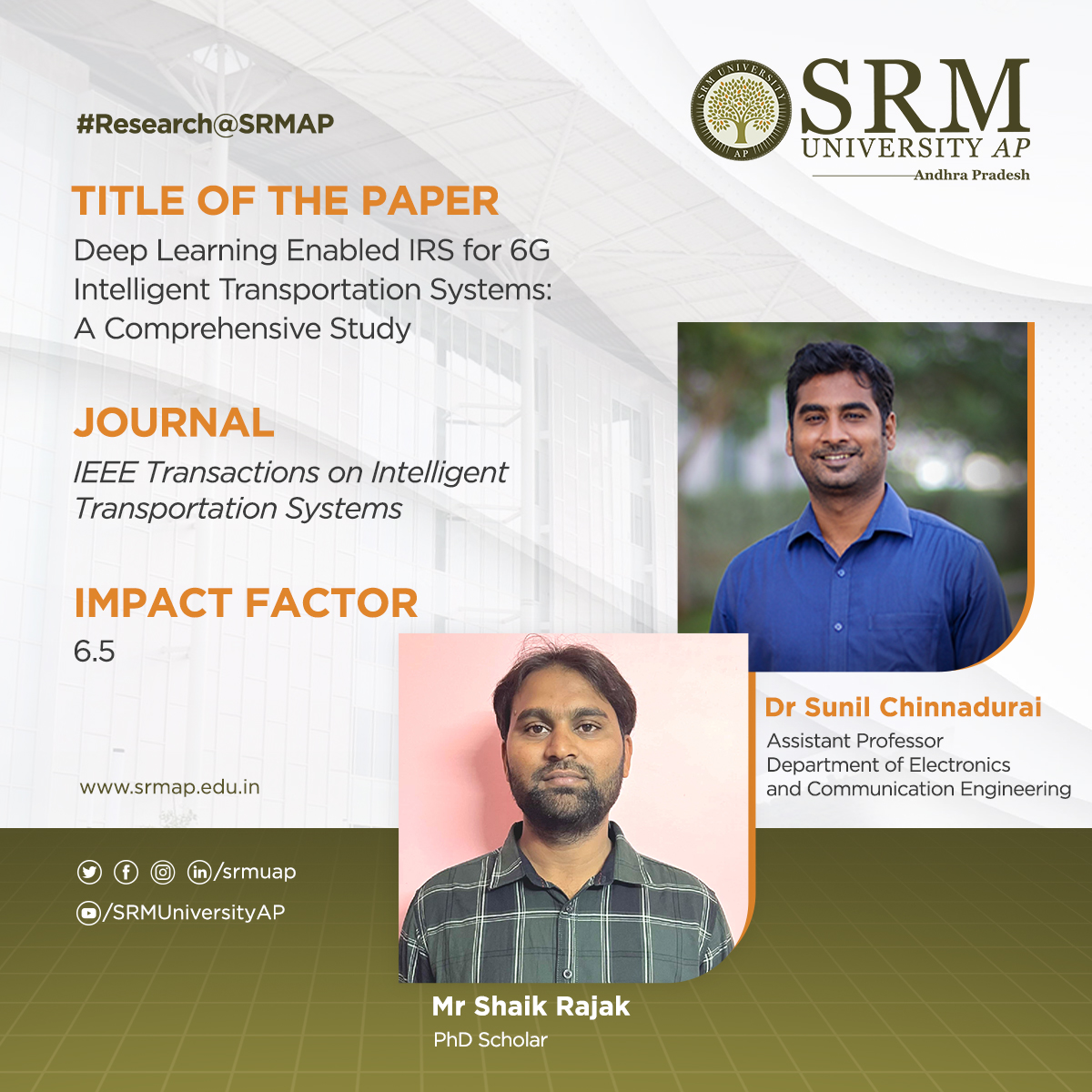

Intelligent Transportation System (ITS) is on its way to becoming the biggest player in the coming-of-age transportation system. However, the sheer demand for the enormous amount of data to secure seamless connectivity and functioning with maximum speed and safety tends to increase the power consumption of the ITS. Dr Sunil Chinnadurai and his PhD scholar Mr Shaik Rajak from the Department of Electronics and Communication Engineering present Intelligent Reflecting Surfaces (IRS) as the key enabling technology to provide the data required by the ITS with less power consumption.

Their article “Deep Learning Enabled IRS for 6G Intelligent Transportation Systems: A Comprehensive Study” which makes a comprehensive study on the DL-enabled IRS-aided ITS was published in the esteemed journal ‘IEEE Transactions on Intelligent Transportation Systems’ having an Impact factor of 6.5. The article elucidates the ways and means to overcome the channel estimation, secrecy rate, and energy efficiency optimisation problems.

The research suggests that connecting ITS to wireless networks via IRS will help in reaching the destination within the stipulated time duration with enhanced safety and comfort. Besides highlighting the reduced power consumption and hardware cost of the DL-enabled IRS-aided ITS, the article also projects that IRS usage in 6G-ITS massively helps the traffic control system to precisely send and receive the information of school buses as well as healthcare vehicles like ambulances, fire safety vehicles, etc. Their future research plans also include the experimental analysis of energy efficiency for wireless networks and Intelligent Transportation Systems with IRS.

Abstract of the Research

Intelligent Transportation Systems (ITS) play an increasingly significant role in our life, where safe and effective vehicular networks supported by sixth generation (6G) communication technologies are the essence of ITS. Vehicle-to-vehicle (V2V) and vehicle-to-infrastructure (V2I) communications need to be studied to implement ITS in a secure, robust, and efficient manner, allowing massive connectivity in vehicular communications networks. Besides, with the rapid growth of different types of autonomous vehicles, it becomes challenging to facilitate the heterogeneous requirements of ITS. To meet the above needs, intelligent reflecting surfaces (IRS) are introduced to vehicular communications and ITS, containing the reflecting elements that can intelligently configure incident signals from and to vehicles. As a novel vehicular communication paradigm at its infancy, it is key to understand the latest research efforts on applying IRS to 6G ITS as well as the fundamental differences with other existing alternatives and the new challenges brought by implementing IRS in 6G ITS. In this paper, we provide a big picture of deep learning enabled IRS for 6G ITS and appraise most of the important literature in this field. By appraising and summarizing the existing literature, we also point out the challenges and worthwhile research directions related to IRS aided 6G ITS.

- Restoring the highly corrupted digital image June 21, 2022

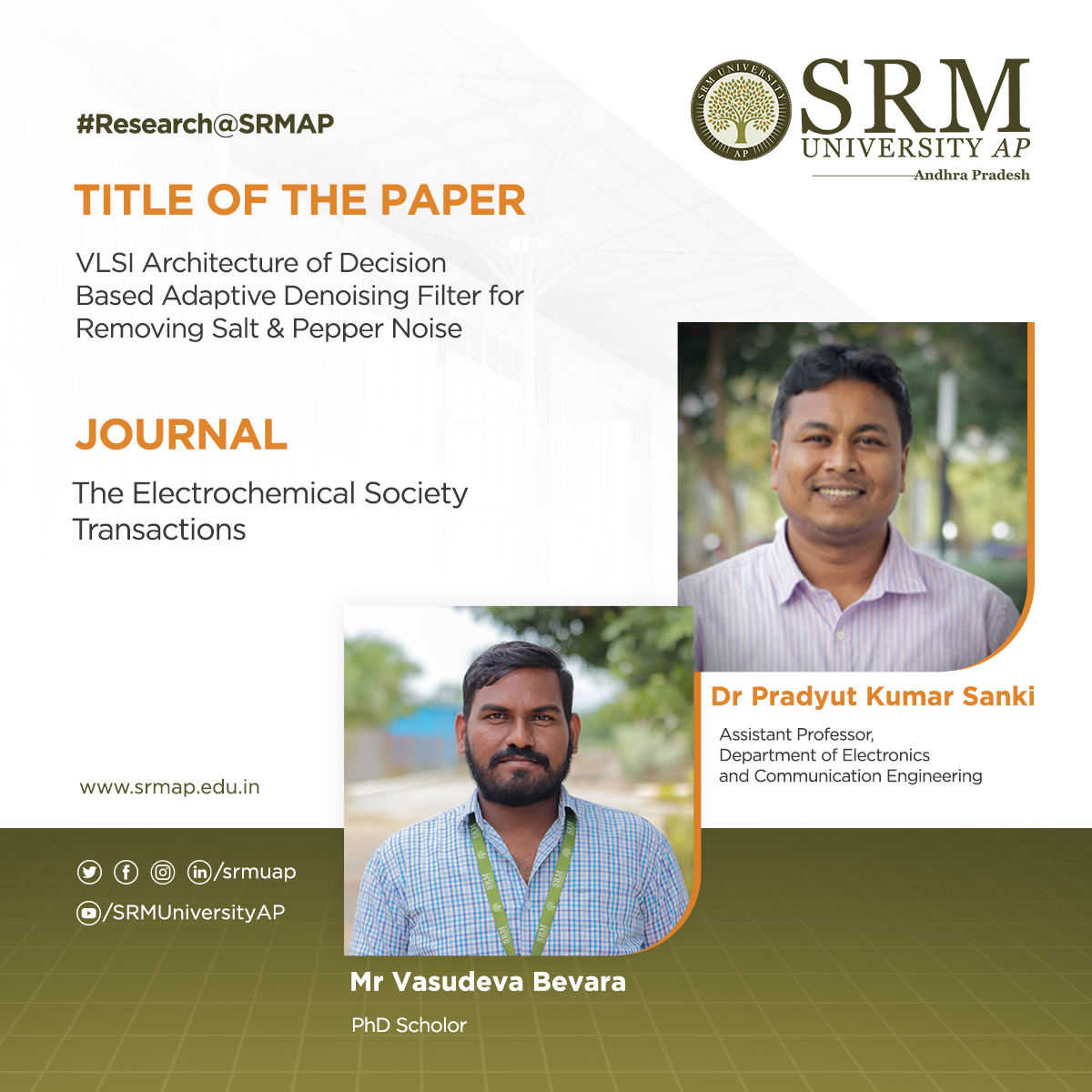

The Electrochemical Society Transactions (ECST) is the official conference proceedings publication of The Electrochemical Society. Recently, a research paper was published in ECST by Mr Vasudeva Bevara, a PhD scholar of the Department of Electronics and Communication Engineering, under the supervision of Assistant professor Dr Pradyut Kumar Sanki. The paper is titled VLSI Architecture of Decision Based Adaptive Denoising Filter for Removing Salt & Pepper Noise and proposes an innovative concept to restore a highly corrupted digital image.

Abstract

Continue reading → A new Decision Based Adaptive Denoising Filter (DBADF) algorithm and hardware architecture are proposed for restoring the digital image that is highly corrupted with impulse noise. The proposed DBADF detects only the corrupted pixels, and that pixel is restored by the noise-free median value or previous value based upon the noise density in the image. The proposed DBADF uses a 3×3 window initially and adaptively goes up to a 7×7 window based on the noise corruption of more than 50% by impulse noise in the current processing window. The proposed architecture was found to exhibit better visual qualitative and quantitative evaluation based on PSNR, IEF, EKI, SSIM, FOM, and error rate. The DBAMF architecture also preserves the original information of digital image with a high density of salt and pepper noise compared to many standard conventional algorithms. The proposed architecture has been simulated using the VIRTEX7 FPGA device, and the reported maximum post place and route frequency are 149.995MHz, and the dynamic power consumption is 179mW.

A new Decision Based Adaptive Denoising Filter (DBADF) algorithm and hardware architecture are proposed for restoring the digital image that is highly corrupted with impulse noise. The proposed DBADF detects only the corrupted pixels, and that pixel is restored by the noise-free median value or previous value based upon the noise density in the image. The proposed DBADF uses a 3×3 window initially and adaptively goes up to a 7×7 window based on the noise corruption of more than 50% by impulse noise in the current processing window. The proposed architecture was found to exhibit better visual qualitative and quantitative evaluation based on PSNR, IEF, EKI, SSIM, FOM, and error rate. The DBAMF architecture also preserves the original information of digital image with a high density of salt and pepper noise compared to many standard conventional algorithms. The proposed architecture has been simulated using the VIRTEX7 FPGA device, and the reported maximum post place and route frequency are 149.995MHz, and the dynamic power consumption is 179mW. - Matrix enabled road distress classification system June 20, 2022

The Department of Electronics and Communication Engineering is glad to announce that Dr V Udaya Sankar, Assistant Professor has published the patent (App no. 202141056542), ‘A system and method with Matrix enabled Road distress classification with reduced computational complexity and reduced memory requirements’, in collaboration with Dr Siva Sankar Yellampalli and Ms Gayathri Lakshmi Chinthakrindi.

This work has applications related to visual inspection systems. While this research considers road crack detection application, the same can be extended to various applications such as leaf disease prediction, covid prediction etc. This invention provides an alternative approach instead of using traditional machine learning algorithms that has less computational complexity as opposed to deep neural networks that take more complex operations. This method will also lead to further research in matrix-based machine learning applications related to image processing and image classification.

The research team is planning to collaborate with Efftronics Systems Pvt ltd. for PCB defect detection and discussions are initiated with some start-ups for visual inspection applications. Their future research plan is to look deeper into these algorithms in combination with some of the deep neural networks to reduce computational complexity. In addition, Dr Udaya Sankar is also looking forward to establishing his own start-up in the incubation centre soon.

Abstract of the Research

A method for image classification is provided, wherein, the pre-processed gray scale image is first sent to the feature extraction block, and the said feature extraction block considers every image as a matrix and computes the metrics for features, viz., 1) EMD distance which is popularly known as Wassertain distance/Earth movers distance and is computed with respect to block image and 2) Frobenius Norm which is the square root of the sum of the absolute squares of its elements and finally, 3) Condition Number, which measures the ratio of the maximum relative stretching to the maximum relative shrinking that matrix does to any non-zero vectors. This method is preferred over the existing methods due to the drastic reduction in computational complexities and, utilizing lesser memory. Also, with this method and system, the communicational complexities too are significantly reduced and also, and the results yielded are far more significantly accurate.

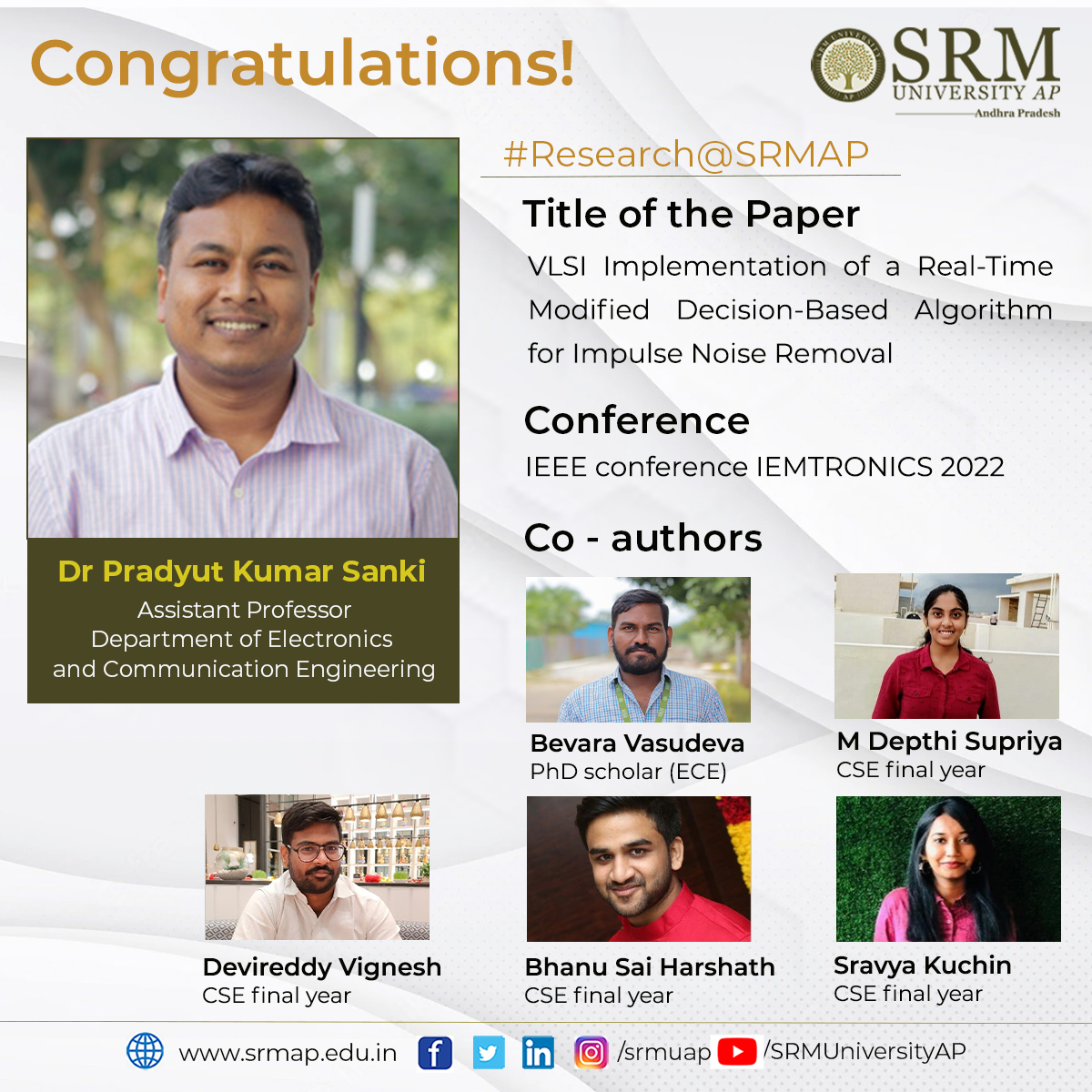

- Research article accepted for IEEE conference IEMTRONICS 2022 June 4, 2022

SRM University-AP preserves a research-empowered ecosystem stimulating its faculty and students to roll out original and discerning studies capable of making instrumental contributions aiming the scientific and societal progress. Making strides with impactful research publications and groundbreaking achievements, the institution has carved a niche for itself in the academic milieu. We are glad to present yet another success story of our research community that keeps bringing laurels to the institutions from far and wide.

Dr Pradyut Kumar Sanki and his PhD scholar Bevara Vasudeva, from the Department of Electronics and Communications Engineering, along with a group of Computer Science and Engineering students: Medarametla Depthi Supriya, Devireddy Vignesh, Peram Bhanu Sai Harshath, and Sravya Kuchina have got their paper titled ‘’VLSI Implementation of a Real-Time Modified Decision-Based Algorithm for Impulse Noise Removal’’ accepted in the IEEE conference IEMTRONICS 2022. This publication is a part of the Capstone project contributed by the students.

IEMTRONICS 2022 (International IOT, Electronics and Mechatronics Conference) is an international conclave that aims to bring together scholars from different backgrounds to disseminate inventive ideas in the fields of IOT, Electronics and Mechatronics. The conference will also promote an intense dialogue between academia and industry to bridge the gap between academic research, industry initiatives, and governmental policies. This is fostered by panel discussions, invited talks, and industry exhibits where academia and industry will mutually benefit from each other.

Through the research paper, the team proposes a real-time impulse noise removal (RTINR) algorithm and its hardware architecture for denoising images corrupted with fixed valued impulse noise.

Abstract of the Research

A decision-based algorithm is modified in the proposed RTINR algorithm where the corrupted pixel is first detected and is restored with median or previous pixel value depending on the number of corrupted pixels in the image. The proposed RTINR architecture has been designed to reduce the hardware complexity as it requires 21 comparators, 4 adders, and 2 line buffers which in turn improve the execution time. The proposed architecture results better in qualitative and quantitative performance in comparison to different denoising schemes while evaluated based on the following parameters: PSNR, IEF, MSE, EKI, SSIM, FOM, and visual quality. The proposed architecture has been simulated using the XC7VX330T-FFG1761 VIRTEX7 FPGA device and the reported maximum post place and route frequency is 360.88 MHz. The proposed RTINR architecture is capable of denoising images of size 512 × 512 at 686 frames per second. The architecture has also been synthesized using UMC 90 nm technology where 103 mW power is consumed at a clock frequency of 100 MHz with a gate count of 2.3K (NAND2) including two memory buffers.

Continue reading →